Содержание

- 2. Общие сведения В процессе обработки многоразрядных двоичных данных в цифровых устройствах возможны две формы представления информации:

- 3. Регистры Регистром (от английского слова to register – регистрировать) называют цифровой узел, основным назначением которого является

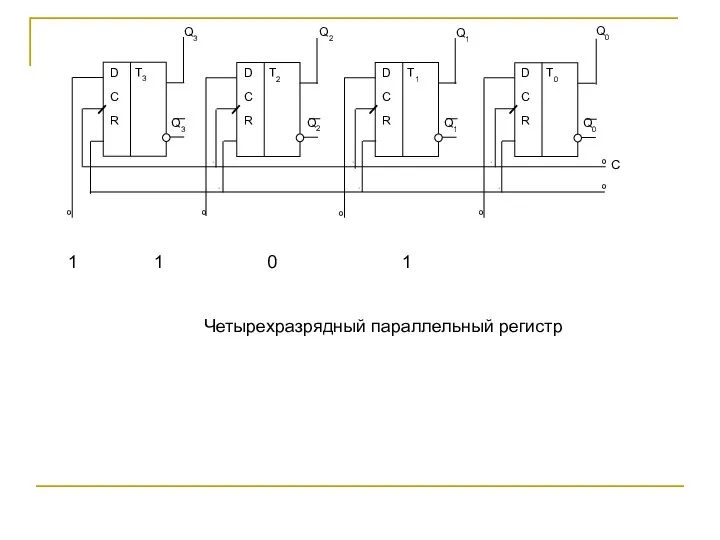

- 4. Параллельные регистры В параллельных регистрах прием и выдача чисел производится по всем разрядам одновременно. На рис.

- 5. 1 1 0 1 Четырехразрядный параллельный регистр

- 6. Условное обозначение микросхемы М530ИР19, представляющею собой 4-разрядный параллельный регистр на D-триггерах. Когда на вход Е подано

- 7. Сдвигающие регистры Сдвигающие регистры предназначены для преобразования информации путем ее сдвига под воздействием тактовых импульсов. Схема

- 8. Вход регистра С, на который поступают импульсы сдвига, образован путем объединения С-входов триггеров, а вход сброса

- 9. Изложенный алгоритм работы сдвигающего регистра в процессе формирования параллельного двоичного кода х3 х2 х1 х0. В

- 10. В процессе работы этого регистра происходит последовательное занесение старшего и последующих битов информации в регистр младшего

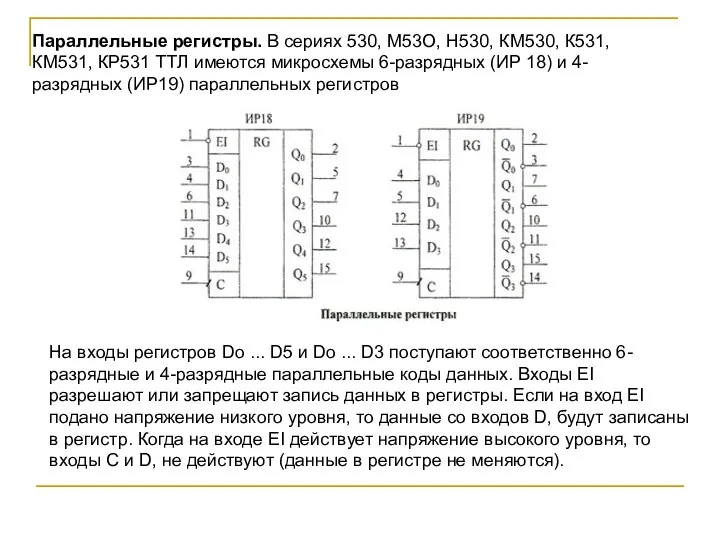

- 11. Микросхемы регистры В сериях интегральных схем имеется много вариантов регистров (только в сериях ТТЛШ их около

- 12. На входы регистров Do ... D5 и Do ... D3 поступают соответственно 6-разрядные и 4-разрядные параллельные

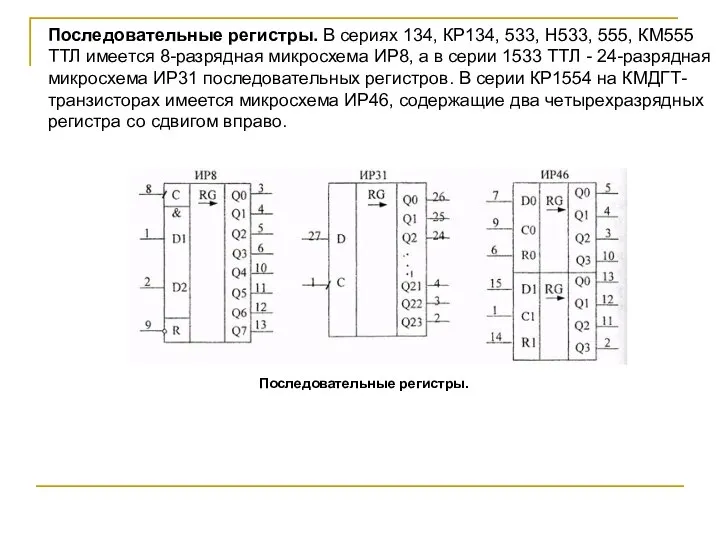

- 13. Последовательные регистры. В сериях 134, КР134, 533, Н533, 555, КМ555 ТТЛ имеется 8-разрядная микросхема ИР8, а

- 14. Особенность регистра ИР8 в том, что его информационные входы Dl, D2 объединены логикой 2И. Если на

- 16. Скачать презентацию

Методики расчёта инсоляции

Методики расчёта инсоляции PO-115_dlya_kuratora_na_pervoe_sentyabrya

PO-115_dlya_kuratora_na_pervoe_sentyabrya Заводоуковский районный Совет ветеранов приглашает школьников принять участие в акции Чистые руки

Заводоуковский районный Совет ветеранов приглашает школьников принять участие в акции Чистые руки Новый домашний тренинг. Практика. День-2. Раздел Тренировки

Новый домашний тренинг. Практика. День-2. Раздел Тренировки Техническое обслуживание и ремонт внутреннего газопровода 5-ти этажного жилого дома

Техническое обслуживание и ремонт внутреннего газопровода 5-ти этажного жилого дома Діні қуатты елдің – іргесі берік

Діні қуатты елдің – іргесі берік Проект по технологии. Моя комната

Проект по технологии. Моя комната Разрядность выходных данных. Лекция 10

Разрядность выходных данных. Лекция 10 МК_Имидж_презентация_Илья

МК_Имидж_презентация_Илья Творческая работа Аквариум

Творческая работа Аквариум Методы обучения истории: общая характеристика

Методы обучения истории: общая характеристика Христианские праздники

Христианские праздники How Often Rule

How Often Rule Волейбол на олимпийских играх

Волейбол на олимпийских играх Тест 1 Класс ЕСТ-НАУЧ. Грамот

Тест 1 Класс ЕСТ-НАУЧ. Грамот Эксплуатация беспилотных авиационных систем

Эксплуатация беспилотных авиационных систем Нежилое помещение г. Нижний Новгород (фото)

Нежилое помещение г. Нижний Новгород (фото) Проведение капитального ремонта магистрального нефтепровода

Проведение капитального ремонта магистрального нефтепровода Development of air conditioning

Development of air conditioning ESD Class 0 Protection Stress Levels

ESD Class 0 Protection Stress Levels Разнообразие яшм горы Полковник

Разнообразие яшм горы Полковник Что растёт на клумбе

Что растёт на клумбе Фигурки

Фигурки Результативность участия 1-3 четв. 2016-2017 учебный год. Фотоальбом

Результативность участия 1-3 четв. 2016-2017 учебный год. Фотоальбом Cfu. Department of obs. & gyn. 1

Cfu. Department of obs. & gyn. 1 Трансформаторы. Электрические машины. Лекция 3

Трансформаторы. Электрические машины. Лекция 3 Сварка углеродистых сталей

Сварка углеродистых сталей Отчет финансовой деятельности РОО Национальная Федерация конькобежцев за 2021 г

Отчет финансовой деятельности РОО Национальная Федерация конькобежцев за 2021 г